ADC Types (Analog-to-Digital Converter Types): SAR vs Delta-Sigma vs Pipeline vs

Global electronic component supplier ERSAELECTRONICS: Rich inventory for one-stop shopping. Inquire easily, and receive fast, customized solutions and quotes.

What are ADC types?

Analog-to-Digital Converter Types: SAR, Delta-Sigma, Pipeline, Flash

The main analog-to-digital converter types—often called ADC types—are SAR, delta-sigma (Σ-Δ), pipeline, flash, and dual-slope (integrating). Each ADC converter architecture trades speed, resolution, latency, power, and interface complexity, so the “best” choice depends on bandwidth and control-loop needs rather than headline bits. If you need a refresher on what is ADC, jump to the hub for a quick definition. For deeper design work—turning nominal bits into ENOB/SNR, preventing aliasing, and moving samples over SPI/LVDS/JESD—use the “Read next” cards below and the type sections that follow.

Quick list of ADC types

SAR

How: Binary search with a DAC and comparator on each sample.

Best: Low-latency sensing, control loops, and multi-channel DAQ.

Delta-Sigma (Σ-Δ)

How: Oversample, noise-shape, then decimate with a digital filter for higher ENOB.

Best: Precision, low-bandwidth sensors, audio, and metering.

Pipeline

How: Split conversion into stages; each stage resolves a few bits in sequence.

Best: High-speed DAQ, IF sampling, and imaging.

Flash (Parallel)

How: Comparator array in a flash type ADC makes a single, one-shot decision.

Best: Ultra-fast triggers where latency outweighs resolution.

Dual-slope / Integrating

How: Integrate the input, then de-integrate against a stable reference.

Best: Very low-rate metering and precision measurements.

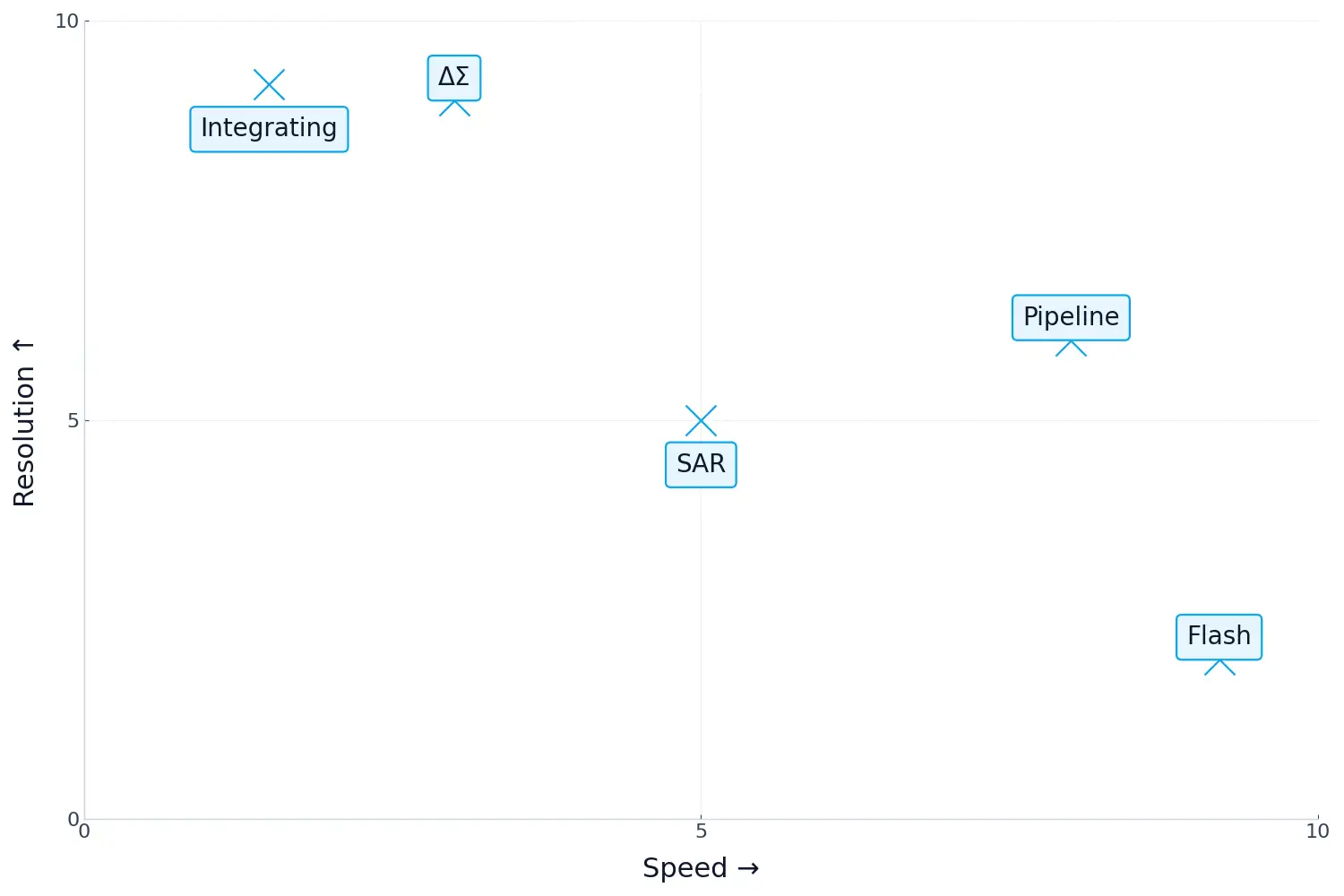

Preview matrix: trade-offs across ADC types

| Type | Speed | Resolution | Latency | Power | Interface | Use-case |

|---|---|---|---|---|---|---|

| SAR | ≈ | ≈ | ✓ | ✓ | ✓ | ✓ |

| Delta-Sigma (Σ-Δ) | — | ✓ | — | ≈ | ≈ | ✓ |

| Pipeline | ✓ | ≈ | ≈ | — | — | ✓ |

| Flash (Parallel) | ✓ | — | ✓ | — | — | ≈ |

| Dual-slope / Integrating | — | ✓ | — | ✓ | ✓ | ≈ |

Details in each type below.

SAR (Successive Approximation)

How: Binary search with an internal DAC and a comparator each sample; the SAR updates its register bit-by-bit until the DAC code matches the held input.

Best for: Low-latency sensing, deterministic control loops, and compact multi-channel DAQ where moderate speed and resolution outweigh extremes.

It’s the general-purpose choice when you need predictable timing, reasonable power, and simple digital integration without heavy filtering or exotic clocks.

Pros

- Very low, deterministic latency

- Power-friendly over wide ranges

- Rich multi-channel / simultaneous options

- Common in MCUs; easy to source

Cons

- Not ideal for extreme bandwidth

- Ultra-high resolution at high speed is hard

- Input driver must settle quickly

Small-batch watch-outs

- Buffer high-impedance sources so the sampling cap fully charges.

- Channel multiplexing cuts effective rate and raises crosstalk—budget per-channel settle time.

- Prioritize local Vref decoupling and clean ground returns before “chasing bits.”

Read next: Resolution / ENOB / SNR, Anti-Aliasing, Interfaces.

Delta-Sigma (Σ-Δ / SDM)

How: Oversample, noise-shape quantization error, then decimate with a digital filter; the modulator pushes noise out of band to raise effective bits.

Best for: Precision at low bandwidth—sensors, audio, and metering—where ENOB trumps real-time control.

Expect excellent small-signal performance and easy averaging, at the cost of group delay and a configuration space that can feel deep for newcomers.

Pros

- Highest ENOB in low bandwidth

- Strong wideband noise rejection

- Digital filters/OSR trade noise for bandwidth

Cons

- Filter group delay hurts fast control loops

- Jitter-sensitive clocking

- Setup adds complexity

Small-batch watch-outs

- Keep PLL/USB/switching noise off clock and Vref paths.

- Validate OSR/filter settings early; they set bandwidth and group delay.

- Don’t chase more bits until reference purity and layout are proven.

Read next: Resolution / ENOB / SNR, Anti-Aliasing, Interfaces.

Pipeline

How: Split conversion into stages; each stage resolves a few bits and passes residue forward, enabling high sample rates with moderate latency.

Best for: Wideband capture—high-speed DAQ, IF sampling, and imaging—when continuous throughput dominates.

It balances speed and resolution but demands disciplined analog drive and clock quality to deliver its datasheet numbers in a real layout.

Pros

- High sample rates with useful resolution

- Deterministic pipeline latency

- Synchronization across multiple channels

Cons

- Higher power and heat

- Demands low-jitter clocks and strong drivers

- Calibration/background correction complexity

Small-batch watch-outs

- Budget driver headroom and acquisition time to meet settling.

- Treat the sampling clock as analog—phase noise maps directly to SNR.

- JESD204/LVDS links add layout, sync, and throughput constraints.

Read next: Interfaces, Anti-Aliasing, Errors & Linearity.

Flash (Parallel)

How: A flash type ADC (parallel) uses a full comparator array against a resistor ladder and decides in a single step—no iteration.

Best for: Situations where absolute minimum latency and trigger certainty outweigh resolution and power concerns.

Think scopes, time-critical discriminators, and capture triggers—not precision measurement or low-power logging.

Pros

- Fastest and truly minimal latency

- Simple, predictable timing at the output

Cons

- Low resolution

- Very high power/area/cost

- Demanding thermal and PDN design

Small-batch watch-outs

- Verify power integrity and heat early; margins disappear quickly at speed.

- Interface throughput may dominate your system budget.

- If latency isn’t existential, consider pipeline or SAR first.

Read next: Interfaces, Anti-Aliasing. FAQ: Why is flash fastest? → fully parallel comparators decide in one step.

Dual-slope / Integrating

How: Integrate the input for a fixed window, then de-integrate against a stable reference; the time ratio maps to the measured value.

Best for: Very low-rate metering and precision measurements that must reject mains ripple and drift.

Unrushed conversions deliver excellent line-frequency immunity and linearity, trading speed for stability and simplicity.

Pros

- Great 50/60-Hz rejection

- Excellent linearity over long windows

- Predictable averaging behavior

Cons

- Very slow conversion

- Unsuitable for dynamic or wideband signals

Small-batch watch-outs

- Budget conversion time in UI/test flow; it’s long by design.

- Guard reference stability and thermal drift; they set accuracy.

- Isolate low-frequency paths from ground loops and EMI.

Read next: Resolution / ENOB / SNR.

Decision Helpers

Most accurate: Delta-Sigma for low bandwidth; real ENOB still depends on Vref noise and layout.

Easiest & most popular: SAR—simple setup, low latency, abundant pin-compatible parts.

Best: Pick by scenario—see Quick Picks.

Micro decision tree (3 steps)

- Highest signal bandwidth / acceptable latency? Go to: Flash (min latency), Pipeline (wideband), SAR (low-latency control).

- Target resolution / ENOB—can you accept decimation delay? Go to: Delta-Sigma (high ENOB at low BW), SAR (no filter group delay).

- Board budget: power, clocking, interface throughput, package? Go to: Pipeline/Flash (if high-speed costs are OK), SAR (MCU-friendly, simpler power/IO).

Ready for parts and alternates? Submit your BOM (48h).

Quick Picks (by scenario)

Slow sensors / metering

Pick Delta-Sigma for high ENOB at low bandwidth.

Stabilize Vref & LF noise; Alt: Integrating for metering.

Control loops / multi-channel DAQ

Pick SAR for low, deterministic latency and easy channel scaling.

Budget settling with MUX; verify per-channel effective rate.

Wideband / IF / imaging

Pick Pipeline for sustained throughput and synchronous capture.

Clock phase noise matters; Alt: Flash for extreme triggers.

FAQ (Types)

Which type of ADC is faster?

A flash type ADC is fastest because a parallel comparator array makes a single-step decision—latency is essentially one comparison window. The trade-off is low resolution and high power/area. Use it for extreme triggers; otherwise consider pipeline for wideband work. Read more: Flash, Pipeline.

Which ADC is most accurate?

For low-bandwidth precision, delta-sigma usually delivers the highest ENOB—thanks to oversampling, noise shaping, and digital filtering. Real accuracy still depends on reference purity, clock quality, and layout, so prove them in measurements before trusting nominal bits. Read more: Delta-Sigma, Resolution.

SAR vs Sigma-Delta: which for control loops?

Pick SAR when you need deterministic, low latency for tight control or multiplexed sensing. Choose delta-sigma when precision dominates and the group delay from digital filtering is acceptable for your loop bandwidth and response targets. Read more: SAR, Delta-Sigma.

Which ADC is easiest in small batches?

SAR parts are easiest to bring up: simple configuration, tolerant input drivers, and abundant pin-compatible options. Watch source impedance and settling when using multiplexers, and prioritize local Vref decoupling before chasing more bits. Read more: SAR.

Can oversampling a SAR match delta-sigma resolution?

Sometimes. Averaging and oversampling can recover a few effective bits, but it costs sampling rate and processing headroom, and real gains are limited by Vref noise, clocking, and layout. Confirm ENOB with code histograms and spectral tests. Read more: Resolution.

Get three safe options in 48 hours

Send your specs or BOM and receive three vetted alternatives—with indicative lead time, price range, and basic front-end/Vref notes.

Cut-Tape / Partial Reel / AEC-Q available.

Related Articles

- ·ICD Electronics: Tiny Lightning, Relentless Reliability

- ·Smart Pill Dispensing Electronics: From Missed Doses to Mission Control

- ·Conditional Access Module (CAM): The Pay-TV Gatekeeper Engineers Actually Enjoy Reading About

- ·NC Formula Semiconductor: The Blockbuster Guide You Didn’t Know You Needed

- ·Electrosurgery Electronics: Turning RF Into a Surgical Superpower

- ·Endoscopic Imaging Electronics: Tiny Optics, Big Picture

- ·Instrument Cluster: The Dashboard Wizard That Makes You Feel Like Iron Man

- ·X-ray & CT Electronics: From Kilovolts to Reconstruction

- ·MRI Core Electronics: From Quench to K-Space

- ·OKL Series PoL DC/DC Converters: The Bite-Size Power Bricks That Keep Your Board Cinematic

.png?x-oss-process=image/format,webp/resize,h_32)